# IGEP<sup>™</sup> SMARC iMX6

# HARDWARE REFERENCE

Document: Revision: Date: MAN-IGEP0046-001 2.0 04/06/2021

# IATEC

ISEE ASSEMBLY TECHNOLOGY.

Av. Cerdanyola 97 08173 - Sant Cugat del Vallès SPAIN +34 93 5763931 info@iseebcn.com <u>https://www.isee.biz/</u>

# **REVISION HISTORY**

| Revision | Date       | Description                          |  |

|----------|------------|--------------------------------------|--|

| 1.0      | 02/26/2016 | Preliminary Release (IGEP 0046-RBxx) |  |

| 1.1      | 03/02/2016 | First Review                         |  |

| 1.2      | 03/10/2016 | SMARC Table Review                   |  |

| 1.3      | 04/23/2016 | Design Changes                       |  |

| 2.0      | 04/06/2021 | Second Review                        |  |

|          |            |                                      |  |

# **CONTENTS**

| R  | VISION     | HISTORY                                               | 2  |

|----|------------|-------------------------------------------------------|----|

| С  | ONTENT     | 5                                                     | 3  |

| LI | ST OF TA   | BLES                                                  | 5  |

| LI | ST OF FI   | GURES                                                 | 6  |

| 1  | USEF       | INFORMATION                                           | 7  |

|    | 1.1        | ABOUT THIS DOCUMENT                                   | 7  |

|    | 1.2        | COPYRIGHT NOTICE                                      | 7  |

|    | 1.3        | TRADEMARKS                                            | 7  |

|    | 1.4        | STANDARDS                                             | 7  |

|    | 1.5        | WARRANTY                                              | 7  |

|    | 1.6        | TECHNICAL SUPPORT                                     | 8  |

| 2  | INTR       | ODUCTION                                              | 9  |

|    | 2.1        | PRODUCT DESCRIPTION                                   | 9  |

|    | 2.2        | IGEP™ SMARC IMX6 BENEFITS AND APPLICATIONS            | 10 |

|    | 2.3        | SMARC STANDARD                                        | 10 |

|    | 2.4        | SMARC FORM FACTOR FEATURE SUMMARY                     | 11 |

|    | 2.5        | IGEP™ SMARC IMX6 SERIES                               | 11 |

|    | 2.6        | PARTS NUMBERS                                         | 12 |

| 3  | HAR        | WARE OVERVIEW                                         | 14 |

|    | 3.1        | IGEP <sup>™</sup> SMARC IMX6                          | 14 |

|    | 3.2        | IGEP™ SMARC IMX6 BLOCK DIAGRAM                        |    |

|    | 3.3        | IGEP™ SMARC IMX6 FEATURES                             |    |

|    | 3.4        | IGEP <sup>™</sup> SMARC IMX6 COMPONENTS MAP           |    |

|    | 3.5        | NXP IMX6 PROCESSORS                                   | 17 |

| 4  | SMA        | RC EXPANSION CONNECTOR INTERFACE                      | 21 |

|    | 4.1        | SMARC INTERFACE DEFINITION                            | 21 |

|    | 4.2        | PINOUT TABLE OF SMARC (VERSION) EXPANSION INTERFACE   |    |

| 5  |            | DUCT SPECIFICATIONSUMMARY                             |    |

| 5  |            |                                                       |    |

|    | 5.1        | POWER SOURCES                                         |    |

|    | 5.1.1      | ,,,, 5                                                |    |

|    | 5.1.2      | - 5                                                   |    |

|    | 5.2        | CONTROL SIGNALS                                       |    |

|    | 5.2.1      |                                                       |    |

|    | 5.2.2      |                                                       |    |

|    | 5.2.3      |                                                       |    |

|    | 5.2.4      | Module State Pins ETHERNET                            |    |

|    | 5.3<br>5.4 | USB CONNECTIONS                                       |    |

|    | 5.4<br>5.5 | I2C: INTER-INTEGRATED CIRCUIT INTERFACE               |    |

|    | 5.5<br>5.6 | SPI: SERIAL PERIPHERAL INTERFACE                      |    |

|    | 5.0<br>5.7 | WIFI/BLUETOOTH AND SD/MMC/SDIO CARD (4 BIT) INTERFACE |    |

|    | 5.8        | UART: ASYNCHRONOUS SERIAL PORTS                       |    |

|    | 5.8<br>5.9 | I2S: SERIAL AUDIO PORT                                |    |

|    | J.J        |                                                       | 50 |

|   | 5.10 | LVDS DISPLAY                       |    |

|---|------|------------------------------------|----|

|   | 5.11 | HDMI DISPLAY                       | 51 |

|   | 5.12 | MIPI-DSI: DISPLAY SERIAL INTERFACE | 53 |

|   | 5.13 | MIPI-CSI: CAMERA SERIAL INTERFACE  | 53 |

|   | 5.14 | SATA                               | 55 |

|   | 5.15 | PCIE: PCI EXPRESS                  | 56 |

|   | 5.16 | CAN BUS: CONTROLLER AREA NETWORK   | 57 |

|   | 5.17 | GPIO: GENERAL PURPOSE INPUT OUTPUT | 58 |

|   | 5.18 | PWM: PULSE-WIDTH MODULATION        | 59 |

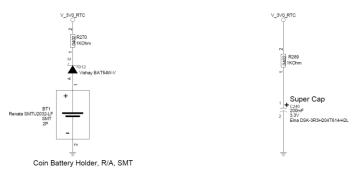

|   | 5.19 | RTC BATTERY                        | 60 |

|   | 5.20 | ENVIRONMENTAL SPECIFICATION        |    |

|   | 5.21 | STANDARDS AND CERTIFICATIONS       |    |

|   | 5.22 | MTBF                               |    |

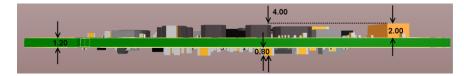

|   | 5.23 | MECHANICAL SPECIFICATION           | 62 |

| 6 | ON-E | BOARD INTERFACES                   | 63 |

|   | 6.1  | SUMMARY                            | 63 |

|   | 6.2  | LEDs                               | 63 |

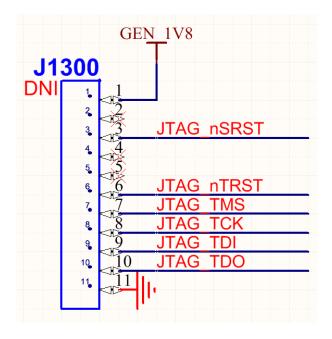

|   | 6.3  | JTAG                               | 64 |

| 7 | ELEC | TRICAL CHARACTERISTICS             | 66 |

| 8 | EXPA | ANSION BOARD                       | 67 |

| 9 | DOC  | UMENT AND STANDARDS REFERENCES     | 69 |

|   |      |                                    |    |

# **LIST OF TABLES**

| Table 1 IGEP™ SMARC iMX6 Ordering Information                    | 13 |

|------------------------------------------------------------------|----|

| Table 2 On-board features                                        | 16 |

| Table 3 Valid SMARC connector part numbers                       | 22 |

| Table 4 SMARC expansion interface information                    | 23 |

| Table 5 Colors Key                                               | 23 |

| Table 6 SMARC pinout description                                 | 34 |

| Table 7 Power Supply pins                                        | 35 |

| Table 8 Digital Ground pins                                      |    |

| Table 9 Boot Mode                                                |    |

| Table 10 Control Signals pins                                    | 41 |

| Table 11 Ethernet pins                                           | 42 |

| Table 12 USB pins                                                | 44 |

| Table 13 I2C pins                                                | 45 |

| Table 14 SPI pins                                                | 47 |

| Table 15 MMC pins                                                | 48 |

| Table 16 UART pins                                               | 49 |

| Table 17 I2S pins                                                | 50 |

| Table 18 LVDS pins                                               |    |

| Table 19 HDMI pins                                               | 52 |

| Table 20 MIPI-DSI pins                                           |    |

| Table 21 MIPI-CSI pins                                           | 54 |

| Table 22 SATA pins                                               | 55 |

| Table 23 PCI3 pins                                               | 57 |

| Table 24 CAN pins                                                | 57 |

| Table 25 GPIO pins                                               | 58 |

| Table 26 PWM pins                                                | 59 |

| Table 27 RTC Battery pin                                         | 60 |

| Table 28 Temperature range                                       | 60 |

| Table 29 Interface summary                                       |    |

| Table 30 LEDs                                                    |    |

| Table 31 JTAG pinout                                             | 65 |

| Table 32 IGEP <sup>™</sup> SMARC iMX6 Electrical Characteristics | 66 |

| Table 33 BASE0040 SMARC EXPANSION Features Rev. D                | 68 |

# **LIST OF FIGURES**

| Figure 1 IGEP™ SMARC iMX6 Possible Part Number                                  | 12 |

|---------------------------------------------------------------------------------|----|

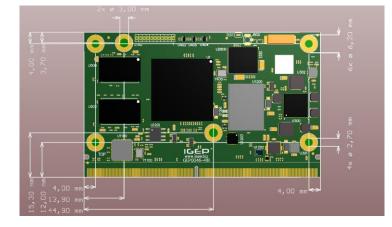

| Figure 2 SMARC iMX6 – Top View                                                  |    |

| Figure 3 SMARC iMX6 – Bottom View                                               | 14 |

| Figure 4 IGEP™ SMARC iMX6 Block Diagram                                         | 15 |

| Figure 5 SMARC iMX6 Components Map                                              | 17 |

| Figure 6 NXP iMX6-DUAL Processors Block Diagram                                 | 17 |

| Figure 7 NXP iMX6-QUAD Processors Block Diagram                                 | 18 |

| Figure 8 NXP iMX6-SOLO Processors Block Diagram                                 | 18 |

| Figure 9 NXP iMX6-DUAL LITE Processors Block Diagram                            | 19 |

| Figure 10 NXP iMX6-DUAL PLUS Processors Block Diagram                           | 19 |

| Figure 11 NXP iMX6-QUAD PLUS Processors Block Diagram                           | 20 |

| Figure 12 SMARC interface area (TOP Side)                                       | 21 |

| Figure 13 SMARC interface area (BOTTOM Side)                                    | 21 |

| Figure 14 SMARC CONNECTOR                                                       | 22 |

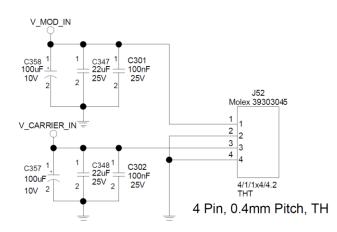

| Figure 15 Power Supply Input circuit                                            | 35 |

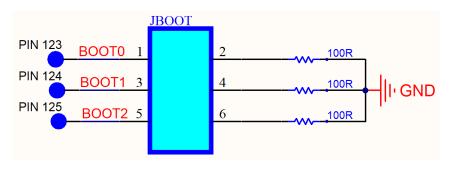

| Figure 16 Boot Mode: jumpers selectors                                          |    |

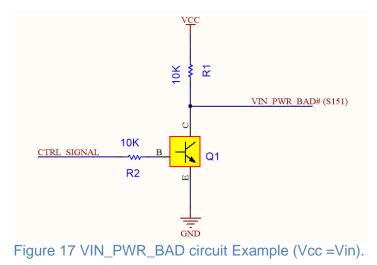

| Figure 17 VIN_PWR_BAD circuit Example (Vcc =Vin).                               | 39 |

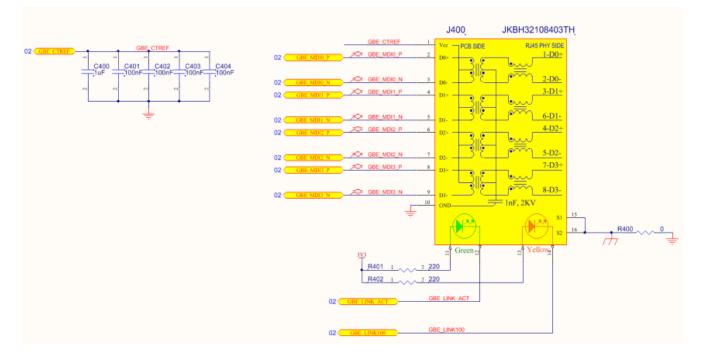

| Figure 18 Ethernet 10/100/1000 Mbps standard circuit                            |    |

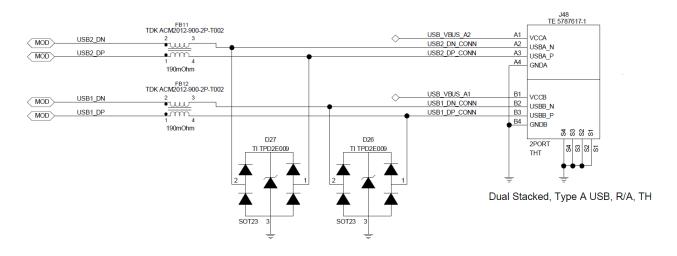

| Figure 19 USB 2.0 Host connections                                              |    |

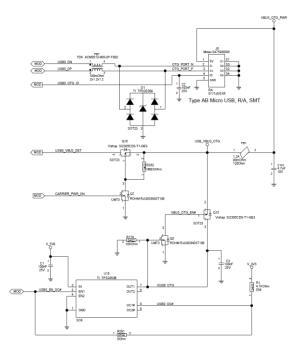

| Figure 20 MicroUSB AB 2.0 OTG connections                                       | 43 |

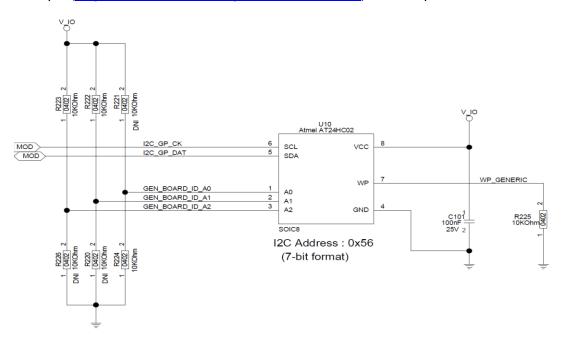

| Figure 21 I2C example: EEPROM connection                                        |    |

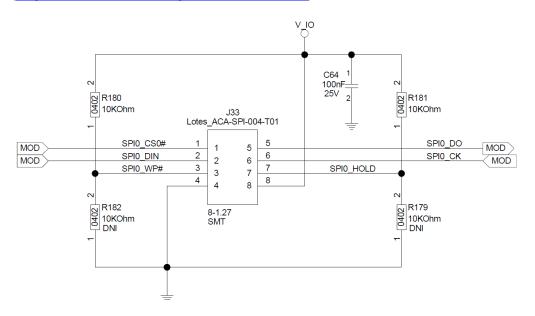

| Figure 22 SPI example: SPI Flash Socket                                         | 46 |

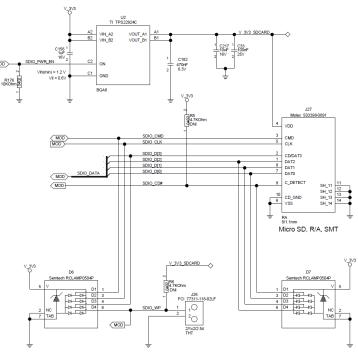

| Figure 23 MMC example: uSD card reader                                          |    |

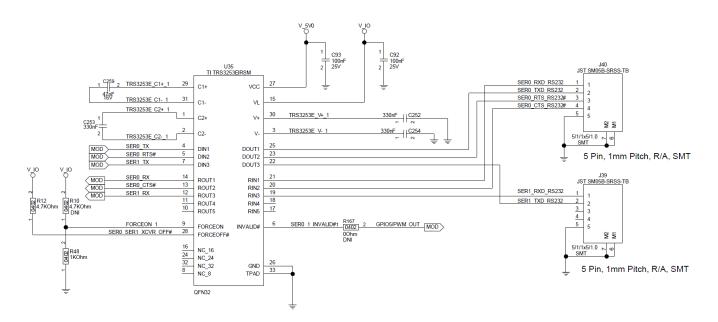

| Figure 24 UART SMARC connections                                                | 48 |

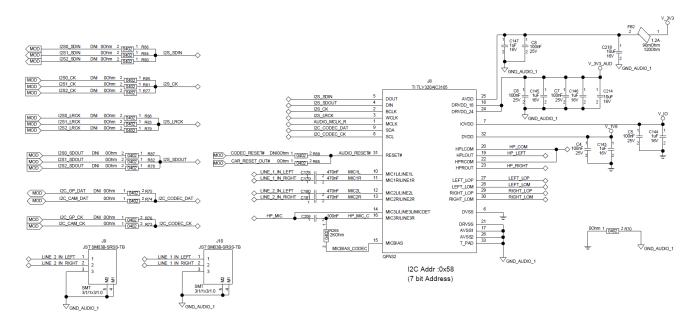

| Figure 25 I2S example: Stereo CODEC with Headphone AMP                          | 50 |

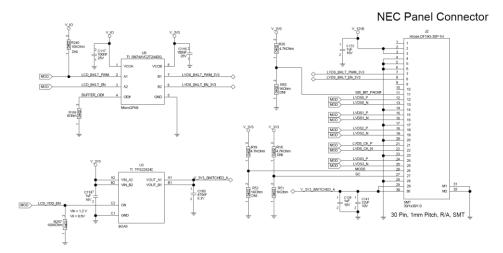

| Figure 26 LVDS connection example                                               |    |

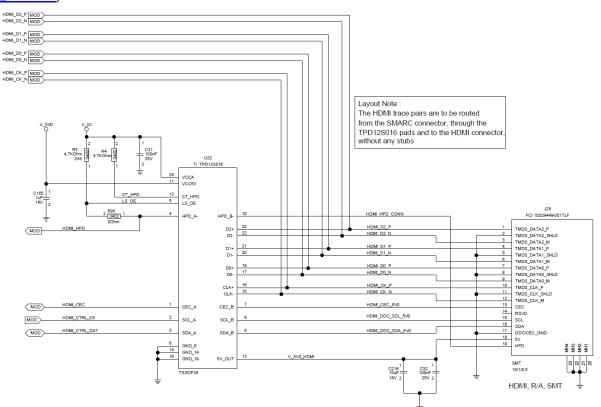

| Figure 27 HDMI connection example                                               |    |

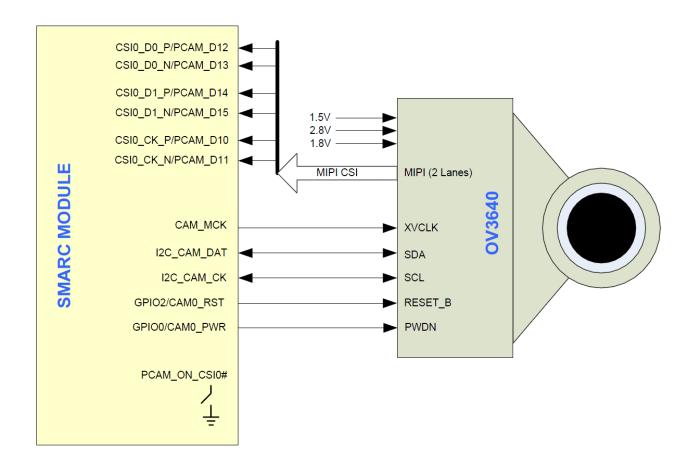

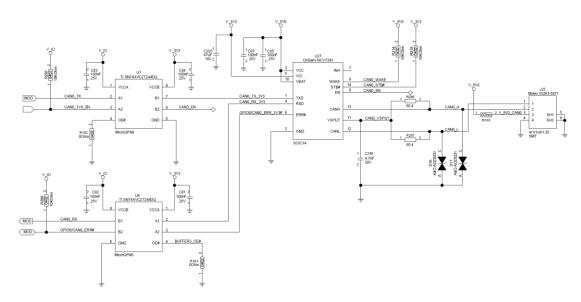

| Figure 28 MIPI-CSI connection example                                           |    |

| Figure 29 SATA connection example                                               | 55 |

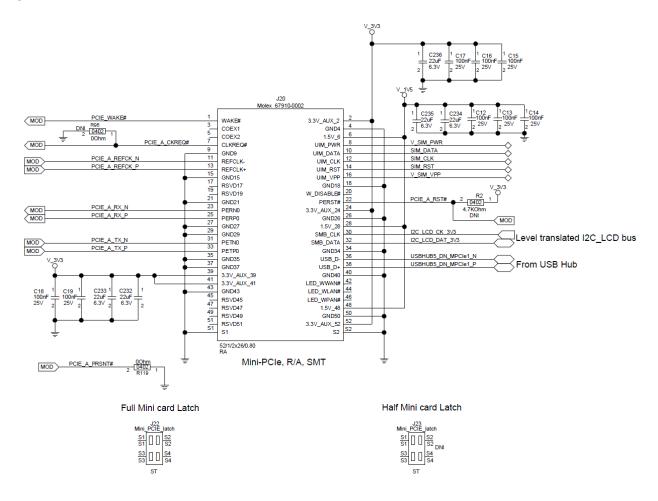

| Figure 30 PCIe connection example                                               | 56 |

| Figure 31 CAN Bus circuit example                                               | 57 |

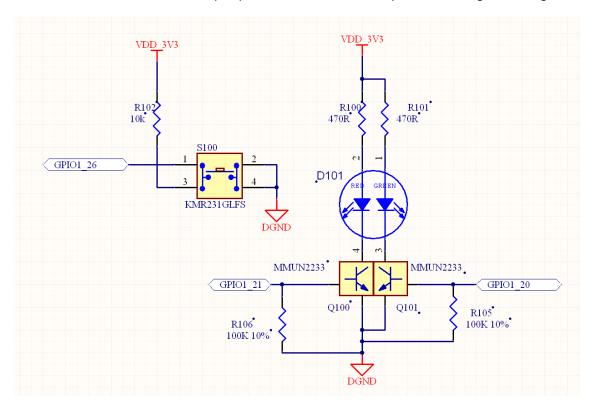

| Figure 32 GPIOs example: control circuit to manage LEDs                         | 58 |

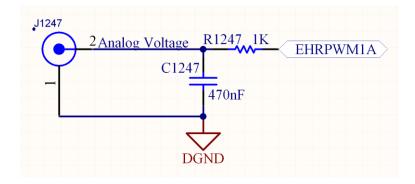

| Figure 33 PWM example: RC filter                                                | 59 |

| Figure 34 RTC Battery                                                           |    |

| Figure 35 IGEP <sup>™</sup> SMARC iMX6 Main Outline Dimensions                  |    |

| Figure 36 IGEP <sup>™</sup> SMARC iMX6 Lateral view Widths Dimensions           |    |

| Figure 37 IGEP <sup>™</sup> SMARC iMX6 side view detailed mechanical dimensions |    |

| Figure 38 LEDs position in the PCB                                              |    |

| Figure 39 JTAG position in the PCB                                              |    |

| Figure 40 JTAG connector schematic                                              |    |

| Figure 41 BASE0040 SMARC EXPANSION Rev. D                                       | 67 |

# **1 USER INFORMATION**

## 1.1 ABOUT THIS DOCUMENT

This document provides information about products from ISEE ASSEMBLY TECHNOLOGY SL and/or its subsidiaries. No warranty of suitability, purpose, or fitness is implied. While every attempt has been made to ensure that the information in this document is accurate, the information contained within is supplied "as-is" and is subject to change without notice.

For the circuits, descriptions and tables indicated, ISEE ASSEMBLY TECHNOLOGY SL assumes no responsibility as far as patents or other rights of third parties are concerned.

## 1.2 COPYRIGHT NOTICE

This document is copyrighted, 2017-2021, by ISEE ASSEMBLY TECHNOLOGY SL.

All rights are reserved. IATEC reserves the right to make improvements to the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of the original manufacturer.

Information provided in this manual is intended to be accurate and reliable. However, the original manufacturer assumes no responsibility for its use, nor for any infringements upon the rights of third parties, which may result from its use.

#### 1.3 TRADEMARKS

IGEP<sup>™</sup> is trademark of IATEC. IATEC is trademark or registered trademark of ISEE ASSEMBLY TECHNOLOGY SL.

Product names, logos, brands, and other trademarks featured or referred to within this user's guide, or the IATEC website, are the property of their respective trademark holders. These trademark holders are not affiliated with IATEC, our products or our website.

### 1.4 STANDARDS

ISEE ASSEMBLY TECHNOLOGY S.L. is going to be certified to ISO 9001:2015.

### 1.5 WARRANTY

#### THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies ISEE ASSEMBLY TECHNOLOGY SL from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

#### EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

7

ISEE ASSEMBLY TECHNOLOGY SL currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive. IATEC assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read specifically, the Warnings and Restrictions notice in this manual prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on IGEP<sup>™</sup> environmental and/or safety programs, please contact with IATEC (support@isee.biz).

No license is granted under any patent right or other intellectual property right of IATEC covering or relating to any machine, process, or combination in which such IATEC products or services might be or are used.

NOTE: It could be found a detailed warranty and sales conditions of IGEP<sup>™</sup> on IATEC website: <u>https://www.isee.biz</u>

#### 1.6 TECHNICAL SUPPORT

Technicians and engineers from ISEE ASSEMBLY TECHNOLOGY SL and/or its subsidiaries are available for technical support. We are committed to make our product easy to use and will help you use our products in your systems.

Please consult our Website at <u>https://www.isee.biz</u> for the latest product documentations: hardware resources (schematics, mechanical drawings, layouts, etc.) and software resources (firmware binaries and sources). You can also contact directly with our Technical Department and we will assist you with any queries or problems you may have (<u>support@isee.biz</u>).

# **2 INTRODUCTION**

## 2.1 PRODUCT DESCRIPTION

The IGEP<sup>™</sup> SMARC iMX6 is an industrial low computer module based on ARM Cortex-A9 at speeds up to 1.2 GHz by NXP iMX6 family of processors.

It is an industrial computer module (it can work in a temperature range from -40°C to +85°C), in a very low profile according the <u>standard form factor SMARC by SGET</u> (its size is only 82,00 mm x 50,00 mm). With different combinations of RAM and Flash memory (see customized possibilities at chapter 2.4) and a complete list of interfaces and peripherals including 3D graphic accelerator, it can be the base for a complex industrial equipment or any other kind of application.

For development purposes there is also available an expansion board (IGEP<sup>™</sup> SMARC EXPANSION) to complete the module. It can be used as the fastest way to develop the user's final application before the prototyping phase. This expansion board can be used with all IGEP<sup>™</sup> SMARC modules.

#### Highlights:

- Fully tested, highly reliable, scalable, efficient and high performing board that allows customers to focus on their end application.

- Designed for industrial range purposes (temperature range: -40 °C to +85 °C).

- Form factor according to small size SMARC (82,00 mm x 50,00 mm).

- Easy connectivity through MXM3 graphic cards type connector: 314-pin, 0,5 pitch right angle.

- 1V8 I/O level signals.

- JTAG interface available.

- Based on NXP iMX6 processor which has an advanced ARM Cortex-A9 core.

- The iMX6 Family processors are based on the enhanced device architecture and include the NEON<sup>™</sup> Media coprocessor.

- One available 10/100/1000 Mbps Ethernet MAC+PHY interface.

- WiFi 802.11 b/g/n / Bluetooth 4.2 connectivity

- RAM memory size: Up to 2 GB.

- Flash memory size: Up to 8 GB eMMC.

- Low Power solution.

- Compatible with SMARC modules.

## 2.2 IGEP<sup>™</sup> SMARC iMX6 BENEFITS AND APPLICATIONS

There are a lot of advantages that developers will find in the IGEP<sup>™</sup> SMARC iMX6 series. Reducing the implementation time and saving costs on their designs. Amongst others, the main benefits are the following:

- Easy scalability between different modules (even with other processors) thanks to the SMARC standard.

- Compact and powerful core for new products.

- Robust and easy to mount due to the MXM3 314-pin connector.

- Reduced time to market.

- Low power consumption  $\leq$  2W.

- Industrial Temperature Range -40 to +85°C.

- Extended life range product.

At the same time, it can be implemented in all kind of end applications. The followings are just a few ones, but the list can be as long as the imagination of the developers.

- Connected vending machines.

- Home / Building automation (IoT applications).

- Human Interface.

- Industrial Control.

- Test and Measurement.

- Artificial Intelligence

### 2.3 SMARC STANDARD

The IGEP<sup>M</sup> SMARC iMX6 accomplish the <u>SMARC 1.1</u> standard with some components of <u>SMARC 2.0</u> <u>version</u>, which is defined <u>by SGET</u>.

The SMARC ("Smart Mobility Architecture") is a computer Module definition targeting applications that require low power, low costs, and high performance. This standard is based on the former ULP-COM standard (Ultra Low Power Computer-on-Modules). The Modules will typically use ARM SoCs (System on Chip) families or similar.

SMARC standard defines two module sizes (82mm x 50mm and 82mm x 80mm). All the available IGEP modules sizes 82mm x 50mm. The Module PCBs have 314 edge fingers that mate with a low profile 314 pin (156 on TOP side and 158 on BOTTOM side) right angle connector. The module pins are designated as P1-P156 on the TOP side and S1 – S158 on the BOTTOM side. The connector is sometimes identified as a 321-pin connector, but 7 pins are lost to the key (4 on the TOP side and 3 on the BOTTOM side).

The Modules are used as building blocks for portable and stationary embedded systems. The core CPU and support circuits, including DRAM, boot flash, power sequencing, CPU power supplies, GBE and a single channel LVDS display transmitter are concentrated on the Module. The modular approach allows scalability, fast time to market and upgradability while still maintaining low costs, low power and small physical size.

## 2.4 SMARC FORM FACTOR FEATURE SUMMARY

Small form factor, low profile and low power edge-finger card format Module with pin-out optimized for ARM and x86 architecture processors; may also be used with low power, tablet oriented X86 and RISC devices.

- Two Module sizes:

- 82mm x 50mm.

- o 82mm x 80mm.

- Carrier Board connector: 314 pin 0.5mm pitch R/A memory socket style connector

- o Originally defined for use with MXM3 graphics cards.

- o SMARC Module pin-out is separate from and not related to MXM3 pin-out.

- Multiple sources for Carrier Board connector.

- Low cost.

- Low profile:

- As low as 1.5mm (Carrier Board top to Module bottom).

- Other stack height options available, including 2.7mm, 5mm, 8mm.

- Overall assembly height (Carrier Board top to tallest Module component) is less than 6mm.

- Excellent signal integrity suitable for 2.5 GHz / 5 GHz / 8 GHz data rate signals such as PCIe Gen 1, Gen 2 and Gen 3.

- Robust, vibration resistant connector.

- Module input voltage range: 3.0V to 5.25V

- Allows operation from 3.6V nominal Lithium-ion battery packs.

- Allows operation from 3.3V fixed DC supply.

- Allows operation from 5.0V fixed DC supply.

- Single supply (no separate standby voltage).

- Module power pins allow 5A max.

- Low power designs

- $\circ$  Fanless.

- Passive cooling.

- Low standby power.

- Design for battery operation.

- 1.8V default I/O voltage.

### 2.5 IGEP™ SMARC iMX6 SERIES

The IGEP<sup>™</sup> SMARC iMX6 series is composed by different models, all of them have the same general circuit but they change in the CPU, the RAM memory, the storage memory and the connectivity used.

In next chapter <u>2.6</u> are commented the main differences according to all models.

Other combinations are available. Contact with IATEC's Sales Department for other configurations.

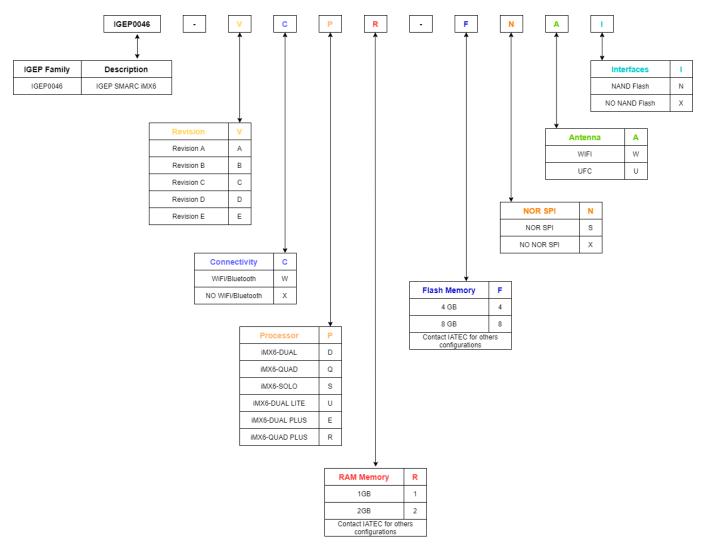

#### 2.6 PARTS NUMBERS

Depending on the module configuration, the module has different parts numbers.

Figure 1 IGEP™ SMARC iMX6 Possible Part Number

| Part Number        | IGEP <sup>™</sup> Device | Description                                                                                                                  |

|--------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| IGEP0046-EWD2-8SXX | SMARC iMX6-DUAL WiFi     | Processor: iMX6 DUAL<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2<br>NOR SPI |

| IGEP0046-EWQ1-8SXX | SMARC iMX6-QUAD WiFi     | Processor: iMX6 QUAD<br>RAM Memory: 1 GB<br>Flash Memory: 8 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2<br>NOR SPI |

| IGEP0046-EWQ2-8SXX<br>IGEP0046-EWS2-8SXX | SMARC iMX6-QUAD WiFi<br>SMARC iMX6-SOLO WiFi | Processor: iMX6 QUAD<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2<br>NOR SPI<br>Processor: iMX6 SOLO<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2 |

|------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGEP0046-EWU1-4XXX                       | SMARC iMX6-DUAL LITE WiFi                    | NOR SPI<br>Processor: iMX6 DUAL LITE<br>RAM Memory: 1 GB<br>Flash Memory: 4 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2                                                                                                                 |

| IGEP0046-EWU1-4XUX                       | SMARC iMX6-DUAL LITE WiFi                    | Processor: iMX6 DUAL LITE<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB<br>Variant without WIFI antenna but UFL connector                                                                                                                             |

| IGEP0046-EWU2-4XXX                       | SMARC iMX6-DUAL LITE WiFi                    | Processor: iMX6 DUAL LITE<br>RAM Memory: 2 GB<br>Flash Memory: 4 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2                                                                                                                            |

| IGEP0046-EWU2-4XXX                       | SMARC iMX6-DUAL LITE NO WiFi                 | Processor: iMX6 DUAL LITE<br>RAM Memory: 2 GB<br>Flash Memory: 4 GB                                                                                                                                                                               |

| IGEP0046-EWU2-8XXX                       | SMARC iMX6-DUAL LITE NO WiFi                 | Processor: iMX6 DUAL LITE<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB                                                                                                                                                                               |

| IGEP0046-EWE2-8SXX                       | SMARC iMX6-DUAL PLUS WiFi                    | Processor: iMX6-DUAL PLUS<br>RAM Memory: 2 GB<br>Flash Memory: 8 GB<br>Connectivity: WiFi 802.11 b/g/n / Bluetooth 4.2<br>NOR SPI                                                                                                                 |

Table 1 IGEP™ SMARC iMX6 Ordering Information.

### **3 HARWARE OVERVIEW**

## 3.1 IGEP<sup>TM</sup> SMARC iMX6

Figure 2 SMARC iMX6 - Top View

Figure 3 SMARC iMX6 - Bottom View

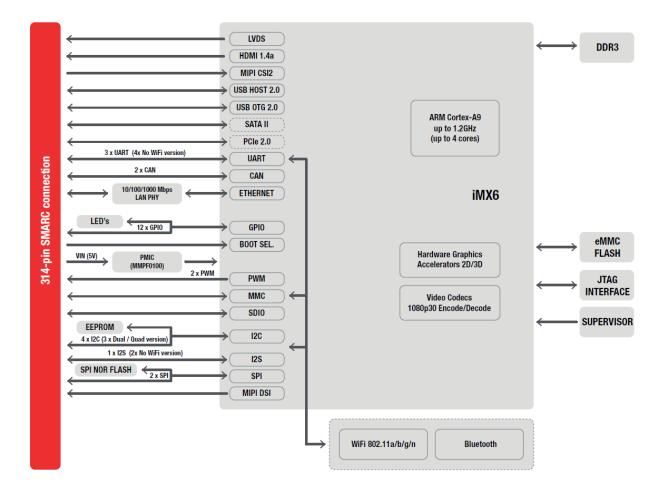

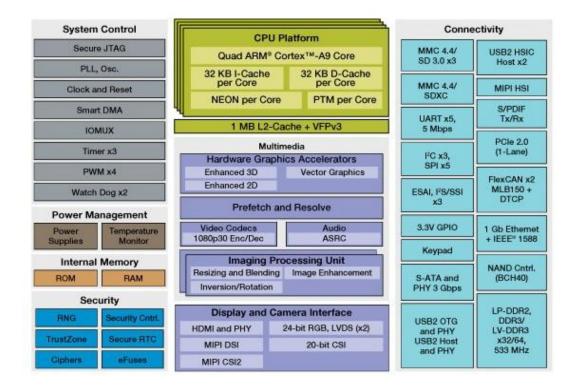

### 3.2 IGEP™ SMARC iMX6 BLOCK DIAGRAM

#### Figure 4 IGEP™ SMARC iMX6 Block Diagram

# 3.3 IGEP™ SMARC iMX6 FEATURES

| Feature             | Specifications                                                               |  |  |

|---------------------|------------------------------------------------------------------------------|--|--|

| Processor           | NXP iMX6                                                                     |  |  |

|                     | CPU: ARM Cortex-A9                                                           |  |  |

|                     | NEON SIMD Coprocessor                                                        |  |  |

|                     | Frequency: 1.2 GHz (1 GHz in SOLO and DUAL LITE versions)                    |  |  |

| Memory              | RAM: Up to 2 GB DDR3                                                         |  |  |

|                     | Flash: Up to 8 GB eMMC                                                       |  |  |

| Camera Interface    | 1 x Parallel Camera 20-bit and 148.5MHz pixel clock                          |  |  |

|                     | Support BT.656 interface                                                     |  |  |

| Display             | 2 x 24-bit Parallel RGB up to WXGA (1366x768) at 60 Hz                       |  |  |

|                     | Support: 24-bit, 18-bit, 16-bit and 8-bit parallel display                   |  |  |

| Digital Audio       | 1 x I2S(SAI) (No WiFi versions: 2x)                                          |  |  |

| Network             | One Ethernet: 10/100/1000 Mbps                                               |  |  |

|                     | WiFi: Certified 802.11 b/g/n (Access Point: Yes)                             |  |  |

|                     | Bluetooth: 4.2                                                               |  |  |

| Antenna             | Internal WiFi/Bluetooth antenna                                              |  |  |

|                     | Optional: U.FL connector for external antenna                                |  |  |

| USB                 | 1 x USB 2.0 OTG (with integrated phy)                                        |  |  |

|                     | 1 x USB 2.0 Host (with integrated phy)                                       |  |  |

| External Interfaces | 3 x UART (No WiFi versions: 4x)                                              |  |  |

|                     | 4 x I2C                                                                      |  |  |

|                     | 1 x HDMI                                                                     |  |  |

|                     | 2 x SPI                                                                      |  |  |

|                     | 2 x CAN                                                                      |  |  |

|                     | 12 x GPIO                                                                    |  |  |

|                     | 1 x JTAG                                                                     |  |  |

|                     | 1 x EEPROM                                                                   |  |  |

| OS Support          | Linux Kernel 4.9                                                             |  |  |

|                     | Distributions: Ubuntu 16.04, Yocto 2.3, Debian                               |  |  |

| Power Supply        | Power from expansion connectors: From 3.0 V to 5,25 V                        |  |  |

|                     | Digital I/O voltage: 1,8 V                                                   |  |  |

| Power Consumption   | 0.32 A                                                                       |  |  |

| Thermal             | Industrial temperature: -40°C to +80°C                                       |  |  |

| Form Factor         | Small SMARC size: 82,00 mm x 50,00 mm                                        |  |  |

| Humidity            | 93% relative Humidity at 40 °C, non-condensing (according to IEC 60068-2-78) |  |  |

| MTBF                | 131400 hours (>15 years)                                                     |  |  |

|                     | Table 2 On board features                                                    |  |  |

Table 2 On-board features

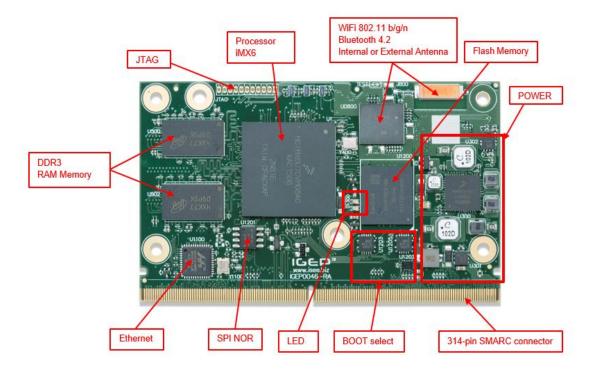

## 3.4 IGEP<sup>™</sup> SMARC iMX6 COMPONENTS MAP

Figure 5 SMARC iMX6 Components Map

# 3.5 NXP iMX6 PROCESSORS

The iMX6-DUAL by NXP is a highly integrated processor based on two ARM Cortex-A9 with a frequency speed of 1.2 GHz (Industrial version).

Figure 6 NXP iMX6-DUAL Processors Block Diagram

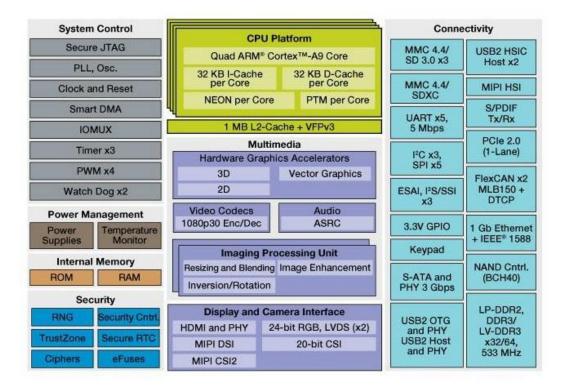

The iMX6-QUAD by NXP is a highly integrated processor based on four ARM Cortex-A9 with a frequency speed of 1.2 GHz (Industrial version).

#### Figure 7 NXP iMX6-QUAD Processors Block Diagram

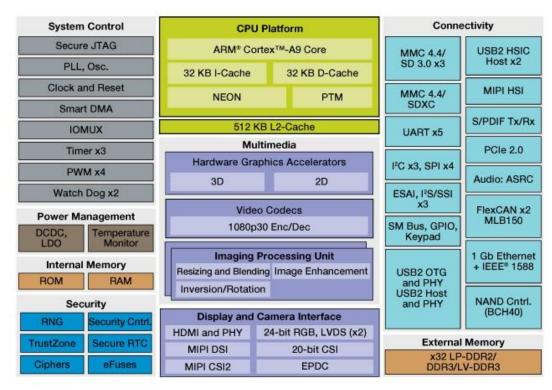

The iMX6-SOLO by NXP is a highly integrated processor based on one ARM Cortex-A9 with a frequency speed of 1 GHz (Industrial version).

Figure 8 NXP iMX6-SOLO Processors Block Diagram

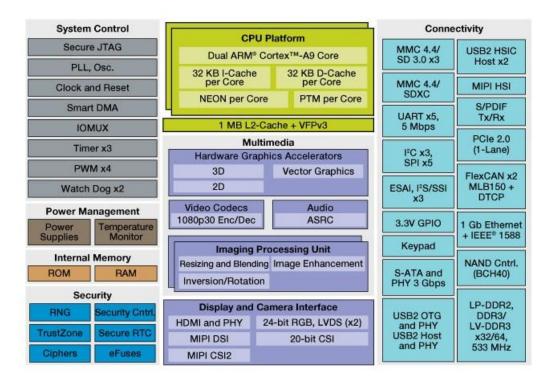

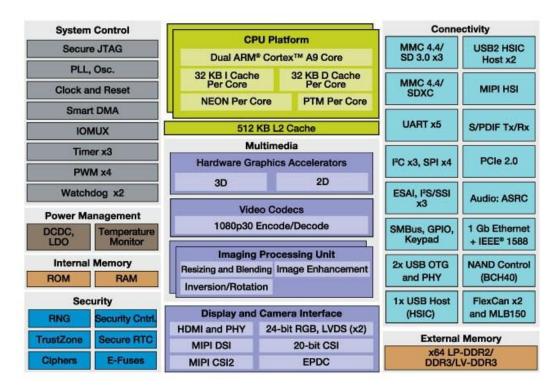

The iMX6-DUAL LITE by NXP is a highly integrated processor based on two ARM Cortex-A9 with a frequency speed of 1 GHz (Industrial version).

#### Figure 9 NXP iMX6-DUAL LITE Processors Block Diagram

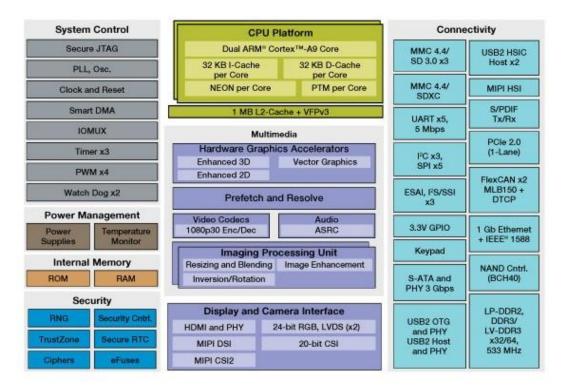

The iMX6-DUAL PLUS by NXP is a highly integrated processor based on two ARM Cortex-A9 with a frequency speed of 1.2 GHz (Industrial version).

Figure 10 NXP iMX6-DUAL PLUS Processors Block Diagram

The iMX6-QUAD PLUS by NXP is a highly integrated processor based on four ARM Cortex-A9 with a frequency speed of 1.2 GHz (Industrial version).

Figure 11 NXP iMX6-QUAD PLUS Processors Block Diagram

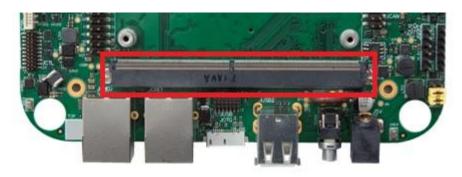

## **4 SMARC EXPANSION CONNECTOR INTERFACE**

#### 4.1 SMARC INTERFACE DEFINITION

IGEP<sup>™</sup> SMARC iMX6 has a 314-pin SMARC interface (156 on TOP side and 158 on BOTTOM side), providing source power and 1V8 CMOS signals to support lots of iMX6 processor features which could be used in custom application. The module sizes are 82mm x 50mm as the SMARC standard defines.

Next figure shows the area and pin numbering of the SMARC interface.

Figure 12 SMARC interface area (TOP Side)

Figure 13 SMARC interface area (BOTTOM Side)

The IGEP<sup>™</sup> SMARC iMX6 modules can be inserted like a target through this SMARC interface to any of the standard connectors existing on the market. Next table shows some valid references (consult <u>the page</u> <u>73 on the SMARC 2.1 Specification</u> to find more information).

| Manufacturer | Part Number       | Height  |  |

|--------------|-------------------|---------|--|

| FOXCONN      | AS0B821-S43B-*H   | 4,3 mm  |  |

| FOXCONN      | AS0B821-S43N-*H   | 4,3 mm  |  |

| FOXCONN      | AS0B826-S43B-*H   | 4,3 mm  |  |

| FOXCONN      | AS0B826-S43N-*H   | 4,3 mm  |  |

| JAE          | MM70-314B2-1-R500 | 4,3 mm  |  |

| Aces         | 91781-314 2 8-001 | 5,2 mm  |  |

| FOXCONN      | AS0B821-S55B-*H   | 5,50 mm |  |

| FOXCONN      | AS0B821-S55N-*H   | 5,50 mm |  |

| FOXCONN      | AS0B826-S55B-*H   | 5,50 mm |  |

| FOXCONN      | AS0B826-S55B-*H   | 5,50 mm |  |

| FOXCONN      | AS0B821-S78B-*H   | 7,80 mm |  |

| FOXCONN      | AS0B821-S78N-*H   | 7,80 mm |  |

| FOXCONN      | AS0B826-S78B-*H   | 7,80 mm |  |

| FOXCONN      | AS0B826-S78N-*H   | 7,80 mm |  |

| Yamaichi     | CN113-314-2001    | 7,80 mm |  |

Table 3 Valid SMARC connector part numbers

Developers must consider the SMARC connector height according to their expansion board needs.

**Note:** Many of the vendor drawings for the connectors listed above show a PCB footprint pattern for use with an MXM3 graphics card. This footprint, and the associated pin numbering, is not suitable for SMARC use. The MXM3 standard gangs large groups of pins together to provide ~80W capable power paths needed for X86 graphics cards.

Figure 14 SMARC CONNECTOR

## 4.2 PINOUT TABLE OF SMARC (VERSION) EXPANSION INTERFACE

This chapter contains all the pinout details for the SMARC-314 expansion interface. The tables below show the meaning of each column in table 6, where is collected all the pins and its main functions.

| COLUMN        | INFORMATION PROVIDED                                                                                                                   |                                                                                          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| PIN           | Indicates the pin number of the SMARC-314 interface. It is either for Primary Side (Top Side, P#) and Secondary Side (Bottom Side, S#) |                                                                                          |

| VOLTAGE LEVEL | Signal Level Voltage                                                                                                                   |                                                                                          |

|               | 5V                                                                                                                                     | 5 V signal                                                                               |

|               | 3V3                                                                                                                                    | 3,3 V signal                                                                             |

|               | 1V8                                                                                                                                    | 1,8 V signal                                                                             |

|               | DS                                                                                                                                     | Differential analog signaling.                                                           |

|               | GBE MDI                                                                                                                                | Differential analog signaling for Gigabit Media Dependent<br>Interface.                  |

|               | PHY MDI                                                                                                                                | Differential analog signaling for FAST Ethernet Media Dependent<br>Interface.            |

|               | TMDS                                                                                                                                   | DVI signaling used for HDMI display interfaces.                                          |

|               | USB                                                                                                                                    | DC coupled differential signaling used for traditional (non-Super-<br>Speed) USB signals |

|               | GND                                                                                                                                    | Digital ground.                                                                          |

|               | RSV                                                                                                                                    | Reserved.                                                                                |

|               | NC                                                                                                                                     | No connected. This pin should be floating.                                               |

| TYPE          | Indicates pin type.                                                                                                                    |                                                                                          |

|               | Power                                                                                                                                  | Power signal.                                                                            |

|               | I CMOS                                                                                                                                 | CMOS input pin.                                                                          |

|               | O CMOS                                                                                                                                 | CMOS output pin.                                                                         |

|               | I/O CMOS                                                                                                                               | CMOS input and output pin.                                                               |

|               | O OD CMOS                                                                                                                              | Open drain output pin.                                                                   |

|               | I/O OD CMOS                                                                                                                            | Open drain input and output pin.                                                         |

|               | NC                                                                                                                                     | No connected. This pin should be floating.                                               |

| MAIN FUNCTION | Main or suggested function                                                                                                             |                                                                                          |

| COMMENTS      | Clarification for the related SMARC-314 interface pin. See device chapter for more information.                                        |                                                                                          |

Table 4 SMARC expansion interface information

| COLORS | INFORMATION                                      |  |

|--------|--------------------------------------------------|--|

|        | Power Sources (Supply Voltages)                  |  |

|        | Signal Level Voltage (Digital and Analog Ground) |  |

|        | Control Signals                                  |  |

|        | Ethernet                                         |  |

|        | USB connections                                  |  |

|        | I2C                                              |  |

|        | SPI                                              |  |

|        | Wifi/Bluetooth and SD/SD card interface          |  |

|        | UART                                             |  |

|        | 12S                                              |  |

|        | LVDS                                             |  |

|        | HDMI                                             |  |

|        | SATA signals                                     |  |

|        | MIPI-DSI                                         |  |

|        | MIPI-CSI                                         |  |

|        | PCle                                             |  |

|        | CAN bus                                          |  |

|        | GPIO                                             |  |

|        | PWM signals                                      |  |

|        | RTC Battery                                      |  |

Table 5 Colors Key

| Pin                | Voltage level | Туре        | Main Function      | Comments                                                                                 |

|--------------------|---------------|-------------|--------------------|------------------------------------------------------------------------------------------|

| Primary (Top) Side |               |             |                    |                                                                                          |

| P1                 | NC            | NC          | PCAM_PXL_CK1       | No connected                                                                             |

| P2                 | GND           | POWER       | GND                | Digital Ground                                                                           |

| P3                 | LVDS D-PHY    | I CMOS      | CSI1_CK+ / PCAM_D0 | CSI1 differential clock input +                                                          |

| P4                 | LVDS D-PHY    | I CMOS      | CSI1_CK- / PCAM_D1 | CSI1 differential clock input -                                                          |

| P5                 | NC            | NC          | PCAM_DE            | No connected                                                                             |

| P6                 | NC            | NC          | PCAM_MCK           | No connected                                                                             |

| P7                 | LVDS D-PHY    | I CMOS      | CSI1_D0+ / PCAM_D2 | CSI1 differential data input D0 +                                                        |

| P8                 | LVDS D-PHY    | I CMOS      | CSI1_D0- / PCAM_D3 | CSI1 differential data input D0 -                                                        |

| P9                 | GND           | POWER       | GND                | Digital Ground                                                                           |

| P10                | LVDS D-PHY    | I CMOS      | CSI1_D1+ / PCAM_D4 | CSI1 differential data inputs D1 +                                                       |

| P11                | LVDS D-PHY    | I CMOS      | CSI1_D1- /PCAM_D5  | CSI1 differential data inputs D1 -                                                       |

| P12                | GND           | POWER       | GND                | Digital Ground                                                                           |

| P13                | LVDS D-PHY    | I CMOS      | CSI1_D2+ / PCAM_D6 | CSI1 differential data input D2 +                                                        |

| P14                | LVDS D-PHY    | I CMOS      | CSI1_D2- / PCAM_D7 | CSI1 differential data input D2 -                                                        |

| P15                | GND           | POWER       | GND                | Digital Ground                                                                           |

| P16                | LVDS D-PHY    | I CMOS      | CSI1_D3+ / PCAM_D8 | CSI1 differential data input D3 +                                                        |

| P17                | LVDS D-PHY    | I CMOS      | CSI1_D3- / PCAM_D9 | CSI1 differential data input D3 -                                                        |

| P18                | GND           | POWER       | GND                | Digital Ground                                                                           |

| P19                | GBE MDI       | I/O CMOS    | GBE_MDI3-          | GB Ethernet pair 3 to magnetics (Media Dependent Interface).                             |

| P20                | GBE MDI       | I/O CMOS    | GBE_MDI3+          | GB Ethernet pair 3 to magnetics (Media Dependent Interface).                             |

| P21                | 1V8           | I/O OD CMOS | GBE_LINK100#       | Active Low. Link Speed Indication LED for GBE0 1000/100 Mbps speed. Inactive if 10 Mbps. |

| P22                | NC            | NC          | GBE_LINK1000#      | No connected                                                                             |

| P23                | GBE MDI       | I/O CMOS    | GBE_MDI2-          | GB Ethernet pair 2 to magnetics (Media Dependent Interface).                             |

| P24                | GBE MDI       | I/O CMOS    | GBE_MDI2+          | GB Ethernet pair 2 to magnetics (Media Dependent Interface).                             |

| P25                | 1V8           | I/O OD CMOS | GBE_LINK_ACT#      | Active Low. Indicates valid link and blinks when there is activity.                      |

| P26                | GBE MDI       | I/O CMOS    | GBE_MDI1-          | GB Ethernet pair 1 to magnetics (Media Dependent Interface).                             |

| P27                | GBE MDI       | I/O CMOS    | GBE_MDI1+          | GB Ethernet pair 1 to magnetics (Media Dependent Interface).                             |

| P28                | NC            | NC          | GBE_CTREF          | No connected                                                                             |

| P29 | GBE MDI | I/O CMOS    | GBE_MDI0-   | GB Ethernet pair 0 to magnetics (Media Dependent Interface).                   |

|-----|---------|-------------|-------------|--------------------------------------------------------------------------------|

| P30 | GBE MDI | I/O CMOS    | GBE_MDI0+   | GB Ethernet pair 0 to magnetics (Media Dependent Interface).                   |

| P31 | 1V8     | O CMOS      | SPI0_CS1#   | iMX6 SPI3 chip select 2 signal                                                 |

| P32 | GND     | POWER       | GND         | Digital Ground                                                                 |

| P33 | 3V3     | I OD CMOS   | SDIO_WP     | MMC1 Write Protect. This signal has a 3K3 PU resistor.                         |

| P34 | 3V3     | I/O CMOS    | SDIO_CMD    | MMC1 Command                                                                   |

| P35 | 3V3     | I OD CMOS   | SDIO_CD#    | MMC1 Card Detect. This signal has a 3K3 PU resistor.                           |

| P36 | 3V3     | O CMOS      | SDIO_CK     | MMC1 Clock                                                                     |

| P37 | 3V3     | O CMOS      | SDIO_PWR_EN | MMC1 Card Power Enable                                                         |

| P38 | GND     | POWER       | GND         | Digital Ground                                                                 |

| P39 | 3V3     | IO CMOS     | SDIO_D0     | MMC1 Data Bus 0                                                                |

| P40 | 3V3     | IO CMOS     | SDIO_D1     | MMC1 Data Bus 1                                                                |

| P41 | 3V3     | IO CMOS     | SDIO_D2     | MMC1 Data Bus 2                                                                |

| P42 | 3V3     | IO CMOS     | SDIO_D3     | MMC1 Data Bus 3                                                                |

| P43 | 1V8     | O CMOS      | SPI0_CS0#   | iMX6 SPI3 chip select 1 signal                                                 |

| P44 | 1V8     | O CMOS      | SPI0_CK     | iMX6 SPI3 clock                                                                |

| P45 | 1V8     | I CMOS      | SPI0_DIN    | iMX6 SPI3 Master Input-Slave Output (MISO)                                     |

| P46 | 1V8     | O CMOS      | SPI0_DO     | iMX6 SPI3 Master Output-Slave Input (MOSI)                                     |

| P47 | GND     | POWER       | GND         | Digital Ground                                                                 |

| P48 | DS      | SATA 3 Gb/s | SATA_TX+    | Differential SATA transmit data +. This signal has a 10 nF coupling capacitor. |

| P49 | DS      | SATA 3 Gb/s | SATA_TX-    | Differential SATA transmit data This signal has a 10 nF coupling capacitor.    |

| P50 | GND     | POWER       | GND         | Digital Ground                                                                 |

| P51 | DS      | SATA 3 Gb/s | SATA_RX+    | Differential SATA receive data +. This signal has a 10 nF coupling capacitor.  |

| P52 | DS      | SATA 3 Gb/s | SATA_RX-    | Differential SATA receive data This signal has a 10 nF coupling capacitor.     |

| P53 | GND     | POWER       | GND         | Digital Ground                                                                 |

| P54 | 1V8     | O CMOS      | SPI1_CS0#   | iMX6 SPI2 chip select 0 signal                                                 |

| P55 | 1V8     | O CMOS      | SPI1_CS1#   | iMX6 SPI2 chip select 1 signal                                                 |

| P56 | 1V8     | O CMOS      | SPI1_CK     | iMX6 SPI2 clock                                                                |

| P57 | 1V8     | I CMOS      | SPI1_DIN    | iMX6 SPI2 Master Input-Slave Output (MISO)                                     |

| P58 | 1V8       | O CMOS     | SPI1_DO iMX6 SPI2 Master Output-Slave Input (MOSI) |                                                                                             |

|-----|-----------|------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|

| P59 | GND       | POWER      | GND                                                | Digital Ground                                                                              |

| P60 | USB       | I/O CMOS   | USB0+                                              | USB1-OTG: USB2.0 differential data input                                                    |

| P61 | USB       | I/O CMOS   | USB0-                                              | USB1-OTG: USB2.0 differential data input                                                    |

| P62 | 3V3       | IO OD CMOS | USB0_EN_OC#                                        | USB1-OTG: Enable (active High)-Overcurrent (active low). This signal has a 3K3 PU resistor. |

| P63 | 5V        | I CMOS     | USB0_VBUS_DET                                      | USB1-OTG: USB host power detection, when this port is used as a device.                     |

| P64 | 3V3       | I CMOS     | USB0_OTG_ID                                        | USB1-OTG: Input Pin to Announce OTG ID (Device Insertion) on USB 2.0 Port, active high.     |

| P65 | USB       | I/O CMOS   | USB1+                                              | USB2: USB2.0 differential data input                                                        |

| P66 | USB       | I/O CMOS   | USB1-                                              | USB2: USB2.0 differential data input                                                        |

| P67 | 3V3       | IO OD CMOS | USB1_EN_OC#                                        | USB2: Enable (active High)-Overcurrent (active low).                                        |

| P68 | GND       | POWER      | GND                                                | Digital Ground                                                                              |

| P69 | NC        | NC         | USB2+                                              | No connected                                                                                |

| P70 | NC        | NC         | USB2-                                              | No connected                                                                                |

| P71 | NC        | NC         | USB2_EN_OC#                                        | No connected                                                                                |

| P72 | NC        | NC         | PCIE_C_PRSNT#                                      | No connected                                                                                |

| P73 | NC        | NC         | PCIE_B_PRSNT#                                      | No connected                                                                                |

| P74 | 3V3       | I CMOS     | PCIE_A_PRSNT#                                      | PCIe Port A: Hotplug presence detect. Active low. Active low                                |

| P75 | 3V3       | O CMOS     | PCIE_A_RST#                                        | PCIe Port A: Port reset output. Active low.                                                 |

| P76 | NC        | NC         | PCIE_C_CKREQ#                                      | No connected                                                                                |

| P77 | NC        | NC         | PCIE_B_CKREQ#                                      | No connected                                                                                |

| P78 | 3V3       | I CMOS     | PCIE_A_CKREQ#                                      | PCIe Port A: clock request input. Active low                                                |

| P79 | GND       | POWER      | GND                                                | Digital Ground                                                                              |

| P80 | NC        | NC         | PCIE_C_REFCK+                                      | No connected                                                                                |

| P81 | NC        | NC         | PCIE_C_REFCK-                                      | No connected                                                                                |

| P82 | GND       | POWER      | GND                                                | Digital Ground                                                                              |

| P83 | LVDS PCIe | O CMOS     | PCIE_A_REFCK+                                      | PCIeA: Differential PCIe Link A reference clock output DC coupled.                          |

| P84 | LVDS PCIe | O CMOS     | PCIE_A_REFCK-                                      | PCIeA: Differential PCIe Link A reference clock output DC coupled.                          |

| P85 | GND       | POWER      | GND                                                | Digital Ground                                                                              |

| P86 | LVDS PCIe | I CMOS     | PCIE_A_RX+                                         | PCIeA: Differential PCIe Link A receive data pair 0.                                        |

| P87 | LVDS PCIe | I CMOS     | PCIE_A_RX-                                         | PCIeA: Differential PCIe Link A receive data pair 0.                                        |

| P88  | GND       | POWER       | GND               | Digital Ground                                                                                     |

|------|-----------|-------------|-------------------|----------------------------------------------------------------------------------------------------|

| P89  | LVDS PCIe | O CMOS      | PCIE_A_TX+        | PCIeA: Differential PCIe Link A transmit data pair 0. This signal has a 0.1 uF coupling capacitor. |

| P90  | LVDS PCIe | O CMOS      | PCIE_A_TX-        | PCIeA: Differential PCIe Link A transmit data pair 0. This signal has a 0.1 uF coupling capacitor. |

| P91  | GND       | POWER       | GND               | Digital Ground                                                                                     |

| P92  | TMDS HDMI | O CMOS      | HDMI_D2+          | HDMI differential pair data input D2 +                                                             |

| P93  | TMDS HDMI | O CMOS      | HDMI_D2-          | HDMI differential pair data input D2 -                                                             |

| P94  | GND       | POWER       | GND               | Digital Ground                                                                                     |

| P95  | TMDS HDMI | O CMOS      | HDMI_D1+          | HDMI differential pair data input D1 +                                                             |

| P96  | TMDS HDMI | O CMOS      | HDMI_D1-          | HDMI differential pair data input D1 -                                                             |

| P97  | GND       | POWER       | GND               | Digital Ground                                                                                     |

| P98  | TMDS HDMI | O CMOS      | HDMI_D0+          | HDMI differential pair data input D0 +                                                             |

| P99  | TMDS HDMI | O CMOS      | HDMI_D0-          | HDMI differential pair data input D0 -                                                             |

| P100 | GND       | POWER       | GND               | Digital Ground                                                                                     |

| P101 | TMDS HDMI | O CMOS      | HDMI_CK+          | HDMI differential clock output pair +                                                              |

| P102 | TMDS HDMI | O CMOS      | HDMI_CK-          | HDMI differential clock output pair -                                                              |

| P103 | GND       | POWER       | GND               | Digital Ground                                                                                     |

| P104 | 1V8       | I CMOS      | HDMI_HPD          | HDMI Hot Plug Detect input. Active low                                                             |

| P105 | 1V8       | I/O OD CMOS | HDMI_CTRL_CK      | I2C2 clock line dedicated to HDMI.                                                                 |

| P106 | 1V8       | I/O OD CMOS | HDMI_CTRL_DAT     | I2C2 bus data dedicated to HDMI. 0x08 is used.                                                     |

| P107 | 1V8       | I/O CMOS    | HDMI_CEC          | HDMI Consumer Electronics Control. Active low                                                      |

| P108 | 1V8       | IO CMOS     | GPIO0 / CAM0_PWR# | General purpose input/output                                                                       |

| P109 | 1V8       | IO CMOS     | GPIO1 / CAM1_PWR# | General purpose input/output                                                                       |

| P110 | 1V8       | IO CMOS     | GPIO2 / CAM0_RST# | General purpose input/output                                                                       |

| P111 | 1V8       | IO CMOS     | GPIO3 / CAM1_RST# | General purpose input/output                                                                       |

| P112 | 1V8       | IO CMOS     | GPIO4 / HDA_RST#  | General purpose input/output                                                                       |

| P113 | 1V8       | IO CMOS     | GPIO5 / PWM_OUT   | PMW Output 1 or General purpose input/output                                                       |

| P114 | 1V8       | IO CMOS     | GPIO6 / TACHIN    | General purpose input/output                                                                       |

| P115 | 1V8       | IO CMOS     | GPIO7 / PCAM_FLD  | General purpose input/output                                                                       |

| P116 | 1V8       | IO CMOS     | GPIO8 / CAN0_ERR# | General purpose input/output                                                                       |

| P117 | 1V8       | IO CMOS     | GPIO9 / CAN1_ERR# | General purpose input/output                                                                       |

| P118                                                 | 1V8                                                         | IO CMOS                                                                     | GPIO10                                                                               | General purpose input/output                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P119                                                 | 1V8                                                         | IO CMOS                                                                     | GPIO11                                                                               | General purpose input/output                                                                                                                                                                                                                                                                                                                                                   |

| P120                                                 | GND                                                         | POWER                                                                       | GND                                                                                  | Digital Ground                                                                                                                                                                                                                                                                                                                                                                 |

| P121                                                 | 1V8                                                         | Ю                                                                           | I2C_PM_CK                                                                            | Power management I2C2 bus clock.                                                                                                                                                                                                                                                                                                                                               |

| P122                                                 | 1V8                                                         | Ю                                                                           | I2C_PM_DAT                                                                           | Power management I2C2 bus data. 0x08 is used.                                                                                                                                                                                                                                                                                                                                  |

| P123                                                 | 1V8                                                         | I OD CMOS                                                                   | BOOT_SEL0#                                                                           | Input straps determine the Module boot device. Active low. See table Table 9.                                                                                                                                                                                                                                                                                                  |

| P124                                                 | 1V8                                                         | I OD CMOS                                                                   | BOOT_SEL1#                                                                           | Input straps determine the Module boot device. Active low. See table Table 9.                                                                                                                                                                                                                                                                                                  |

| P125                                                 | 1V8                                                         | I OD CMOS                                                                   | BOOT_SEL2#                                                                           | Input straps determine the Module boot device. Active low. See table Table 9.                                                                                                                                                                                                                                                                                                  |

| P126                                                 | 1V8                                                         | OUT                                                                         | RESET_OUT#                                                                           | General purpose reset output to Carrier board. Active low                                                                                                                                                                                                                                                                                                                      |

| P127                                                 | 1V8                                                         | IN                                                                          | RESET_IN#                                                                            | Reset input from Carrier board. Active low                                                                                                                                                                                                                                                                                                                                     |

| P128                                                 | 1V8                                                         | IN                                                                          | POWER_BTN#                                                                           | Power-button input from Carrier board. Active low                                                                                                                                                                                                                                                                                                                              |

| P129                                                 | NC                                                          | NC                                                                          | SER0_TX                                                                              | No connected                                                                                                                                                                                                                                                                                                                                                                   |

| P130                                                 | NC                                                          | NC                                                                          | SER0_RX                                                                              | No connected                                                                                                                                                                                                                                                                                                                                                                   |

| P131                                                 | NC                                                          | NC                                                                          | SER0_RTS#                                                                            | No connected                                                                                                                                                                                                                                                                                                                                                                   |

| P132                                                 | NC                                                          | NC                                                                          | SER0_CTS#                                                                            | No connected                                                                                                                                                                                                                                                                                                                                                                   |

| P133                                                 | GND                                                         | POWER                                                                       | GND                                                                                  | Digital Ground                                                                                                                                                                                                                                                                                                                                                                 |

| P134                                                 | 1V8                                                         | O CMOS                                                                      | SER1_TX                                                                              | UART2: Asynchronous serial port 2 data out.                                                                                                                                                                                                                                                                                                                                    |

| P135                                                 | 1V8                                                         | I CMOS                                                                      | SER1_RX                                                                              | UART2: Asynchronous serial port 2 data in.                                                                                                                                                                                                                                                                                                                                     |

| P136                                                 | 11/0                                                        |                                                                             |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | 1V8                                                         | O CMOS                                                                      | SER2_TX                                                                              | UART2: Asynchronous serial port 3 data out.                                                                                                                                                                                                                                                                                                                                    |

| P137                                                 | 1V8<br>1V8                                                  | O CMOS<br>I CMOS                                                            | SER2_TX<br>SER2_RX                                                                   | UART2: Asynchronous serial port 3 data out.<br>UART2: Asynchronous serial port 3 data in.                                                                                                                                                                                                                                                                                      |

| P137<br>P138                                         |                                                             |                                                                             |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | 1V8                                                         | I CMOS                                                                      | SER2_RX                                                                              | UART2: Asynchronous serial port 3 data in.                                                                                                                                                                                                                                                                                                                                     |